Referat Ram (sram, dram, sip, sdram, drdram, ddr)

RAM

Random Access Memory

"640 KB ought to be enough for anybody. " (Bill

Gates, 1981)

Kurs: Informatik

Leistungskurs

Gliederung:

. Speicherarten

o SRAM (Static Random Access Memory)

o DRAM (Dynamic random access memory)

o SIP (Single Inline Package) und SIMM

(Single Inline Memory Module)

o PS/2 (Personal System/2) SIMM

o FPM (Fast Page Mode) DRAM und EDO (Extended Data Output) DRAM

o SDRAM (Synchronous Dynamic Random Access Memory)

o DRDRAM (Direct Rambus DRAM)

o DDR (Double Data Rate) SDRAM

. Speicherangaben

o PC2100, PC2700, PC4300 usw.

o Parity/non-Parity RAM

o ECC (Error Checking and Correcting) und

Chipkill

o Registered, buffered und un-buffered

. Speicherzugriff

. Zukünftiger Speicher

Speicherarten

SRAM (Static Random Access Memory)

Anders als der Name

vermuten lässt ist SRAM auch

flüchtig und kann somit keine Daten ohne Strom speichern. Das "Static" bezieht sich darauf das SRAM im Gegensatz zu

DRAM keine Auffrischungssignale benötigt. Eine SPAM Speicherzelle (1 Bit) speichert

die Daten dabei in einem Flip-Flop der wiederum

durch 4 Transistoren angesteuert wird

(insgesamt 6

Transistoren). Einerseits

bietet SRAM sehr schnelle Zugriffszeiten, andererseits wird im Vergleich zu

DRAM deutlich mehr Platz benötigt. Somit

ist SRAM für einen großen Arbeitsspeicher eher ungeeignet. Heutzutage findet SRAM aufgrund der schnellen

Zugriffszeiten seine Anwendung vor allem als

Cache.

DRAM (Dynamic random access memory)

DRAM speichert die Daten in ebenfalls 1 Bit großen

Speicherzellen, jedoch nicht in

einem Flip-Flop sondern in einem Kondensator

der über einen Transistor angesteuert werden kann.

Heutzutage verwendet man einen

Feldeffekttransistor dessen geringe Eigenkapazität

den Kondensator ersetzt. Dadurch dass der Kondensator sich jedoch ständig entlädt muss

er auch kontinuierlich aufgefrischt werden (3

ms - 64 ms). Durch die

Verwendung von

Kondensatoren und den damit notwendigen Auffrischungen ist DRAM langsamer als SRAM, jedoch ist eine DRAM

Speicherzelle 10-20 mal kleiner als eine

SRAM Zelle. Somit lässt sich deutlich mehr Speicher auf

kleinerem Raum (geringere Kosten) unterbringen.

SIP (Single Inline Package) und SIMM (Single Inline Memory Module) Ursprünglich

wurden die DRAM ICs (DIL genannt)

direkt auf das Motherboard gelötet oder gesteckt. Als jedoch die Speichermengen größer wurden (> 1MB) und somit

der Platz auf den

Motherboard

immer geringer hat man

sich unter anderen auch aus Flexibilitätsgründen dafür

entschieden komplette Module zu bauen. So wurden 1982 erstmals SIP Module produziert. Die SIP Module wurden über 30 Pins

auf das Motherboard gesteckt, man

erkannte allerdings schnell das Pins als Verbindung schlecht geeignet sind da sie leicht abbrechen können

und man die Module Falsch herum einstecken konnte. Daher hat man ~1 Jahr später (1983) die SIMM Module eingeführt, sie waren aus

technischer Sicht baugleich mit den SIP Modulen, hatten jedoch anstelle

der Pins erstmals Kontakte wie man sie heute kennt. Die Zugriffszeiten

lagen zwischen 60 ns und 100 ns. Die Größe lag zwischen 256 KB und 4MB, wobei

die 1MB Module am häufigsten zu

finden waren. Die Datenbusbreite lag

bei 8 Bit, bei einem 286er (16

Bit) Computer musste

man immer 2 gleiche Module verwenden, bei einem 486 (32 Bit)

musste man

somit immer 4

gleiche Module einbauen.

PS/2 (Personal System/2) SIMM

Mit der Einführung der neuen 32 Bit Prozessoren (368 DX und 486) im Jahr 1992 wurde auch mehr Speicher benötigt. Somit baute man

nun komplette 32 Bit Module mit 72

Pins. Der Vorteil lag darin das man

sie nicht mehr in 4er Gruppen

betreiben musste Da sie aber immer

noch auf SIMM Modulen basierten lagen die Zugriffszeiten weiterhin zwischen 60

ns und 70 ns. Die Module wurden in den Größen 4 bis 32 MB hergestellt.

FPM (Fast Page Mode) DRAM und EDO (Extended Data Output) DRAM FPM wurde 1987 eingeführt

und ist eine Technologie die SIMM

Speicher um bis zu 20% beschleunig.

DRAMs sind in Seiten (Pages) unterteilt.

Jeder dieser Seiten ist wiederum in

Zeilen

und Spalten unterteilt. Im Fast Page Modus wurde bei

aufeinanderfolgenden Lese- und

Schreibzugriffen auf eine Zeile innerhalb derselben Seite im DRAM die immer wiederkehrende

Zeilenangabe weggelassen und nur die

Spaltenadresse übertragen. Dadurch

sind kürzere Zugriffszeiten bei zusammenhängenden Daten möglich. Sowohl die alten 30, als auch die 72 Pin

Module wurden mit dem FPM ausgestattet.

Eine weitere eher geringfügige Weiterentwicklung war der 1995 eingeführte

EDO DRAM (auch bekannt als Hyper Page Mode DRAM). Im Hyper Page Mode wurde die nächste Spaltenadresse

bereits während dem Auslesen gesendet, dadurch entstand eine weitere Zugriffszeitenreduzierung von

bis zu 30 %. Durch den annährend gleichen Preis von EDO und FPM Speicher

verdrängte der EDO Speicher den FPM Speicher jedoch relativ schnell.

SDRAM (Synchronous Dynamic Random Access Memory)

Mit dem Pentium I wurde auch ein erweiterter Datenbus von 64 Bit eingeführt, dies machte es

wiederum nötig z.B. zwei gleiche 32 Bit EDO RAM Module zu

verbauen. Zusätzlich wurde der mit maximal

66 Mhz getaktete EDO RAM auch zu

langsam für die neuen Prozessoren.

Aus diesem Grunde hat man den SDRAM eingeführt, das besondere war das er synchron mit dem Systembus

lief. Außerdem waren SDRAMs die

ersten Speichermodule die als DIMM

(Dual Inline Memory Module) gefertigt

wurde, d h. das im Gegensatz zu den SIMMs an den Pins auf Vorder- und Rückseite verschiedene Signale anliegen. Anfangs wurde SDRAM noch

mit 5.0 V betrieben, später jedoch mit 3,3 V. Durch die Kopplung an den Systembus ließen sich Zugriffszeiten von 7 ns -

15 ns erreichen. Eine weitere Neuheit war die Einführung des SPD (Serial

Presence Detect) EEPROMs, dies enthielt alle

notwendigen Daten des Speichermoduls und wurde vom BIOS zur automatischen Konfiguration ausgelesen.

Zusätzlich zu den normalen normale

DIMMs mit 168 Pins wurden auch kompaktere SO- DIMMs (Small Outline) mit 72 Pins (32 Bit) bzw. 144 Pins (64 Bit) zur Verwendung in

Notebooks hergestellt. SDRAM wurde

für Taktraten von 66 Mhz, 100 Mhz, 133 Mhz sowie

150/166 Mhz hergestellt.

DRDRAM (Direct Rambus DRAM)

DRDRAM wurde im Jahr 1999 eingeführt und sollte SDRAM ablösen. DRDRAM ermöglichte deutlich höhere Taktraten (von 300 Mhz bis zu 1066 Mhz), bei einer Datenbusbreite von

lediglich 16 Bit. Zusätzlich wurde die

Spannung auf 2,5 V gesenkt. Es gibt

DRDRAM sowohl als 168 als auch 184 Pin Variante. Des Weiteren verwendet DRDRAM erstmalig die DDR Technologie, womit praktisch der doppelte Takt erreicht

werden konnte. Später kam dann Dual

DRDRAM hinzu womit sich der Datenbus (und somit auch die Transferraten) auf 32 Bit

verdoppelten. Vor allem durch die hohen Lizenzgebühren und den damit verbundenen höheren Endkosten setzte sich DRDRAM jedoch nicht durch.

DDR (Double Data Rate) SDRAM

Ende 1999 erschien DDR

SDRAM, dabei wurde der 64 Bit Datenbus beibehalten und der Takt nur leicht

erhöht (bis zu 200 Mhz). DDR SDRAM

läuft auch mit 2,5 V, konnte jedoch

die kurzen Zugriffszeiten des SDRAMs beibehalten. Wie der Name

schon verdeutlich wurde ebenfalls die DDR (Double Data Rate) Technologie

verwendet. Dabei werden nicht nur bei der aufsteigenden, sondern auch bei der abfallenden Flanke des

Taktsignals Daten übertragen.

Um den Takt

nicht verdoppeln zu müssen wird die sogenannte "Prefetch"

Technik verwendet, dabei werden bei der aufsteigenden Flanke direkt die doppelten Daten gelesen. Die erste

Hälfte wird direkt ausgegeben, die andere wird erst mit

der fallenden Flanke ausgegeben. Zusätzlich zu dem normalen DDR Speicher

gibt es noch DDR2-, sowie DDR3 Speicher.

Dabei wird der Speicher weiterhin

mit demselben Takt betrieben, jedoch

wird anstelle des Zweifach-Prefetch, mit einem Vierfach- bzw. Achtfach-Prefetch gearbeitet. Lediglich der I/O Takt wird

entsprechend erhöht. Die Spannung

der DDR2/3 Module wurde ebenfalls auf

1,8 V bzw. 1,5V gesenkt, dadurch sind sie auch besonders für den mobilen Einsatz geeignet. DDR

Speicher gibt es mit

240 Pins (DIMM), 200 Pins (SO-DIMM) und 214 (Micro-DIMM). Genauso wie für

DRDRAM gibt es auch f r DDR RAM Dual-Channel Speicherkontroller.

Speicherangaben

PC2100, PC2700, PC4300 usw.

Ursprünglich wurde auf diese Weise der Takt des

Speichermoduls angegeben, z.B. PC133

für SDRAM mit 133 Mhz Takt. Seit

der Einführung der DDR Technologie ist man wohl auch unter anderem aus Marketingtechnischen Gründen dazu

übergegangen die gerundete Bandbreite der Module anzugeben.

Bandbreite in Byte = (Speichertakt * Datenbusbreite * DDR Prefetch Wert) / 8

z.B. DDR333 Modul: (166.000.000 Hz * 64 Bit * 2) / 8

= 2.656.000.000 Byte/s = PC2700

Zusätzlich wird DDR2/3 Speicher als PC2 bzw. PC3

angegeben.

Parity/non-Parity RAM

Gibt an ob das Speichermodul über Paritätsbits verfügt. Pro 8 Bit Datenbusbreite wurde

ein Paritätsbit hinzugefügt, dies ermöglichte durch eine einfache Fehlererkennung (keine

Fehlerkorrektur). Dazu wurde einfach geprüft ob es sich um eine gerade oder ungerade Anzahl an er Bits handelt.

ECC (Error Checking and Correcting) und Chipkill

Wie der Name schon vermuten lässt handelt es sich dabei um eine Fehlerkorrektur. Im Gegensatz zu dem älteren Paritätsbits werden die Fehler auch direkt von dem Speichermodul

korrigiert. ECC war nur in der Lage

einzelne Bit Fehler zu korrigieren, daher wurde Chipkill entwickelt was in der Lage ist

auch Multi-Bit Fehler zu korrigieren. Da die Produktion heutzutage schon sehr

ausgereift ist, ist eine Fehlerkorrektur nur

noch in Ausnahmefällen nötig, z.B.

bei Servern mit extrem hohem Datendurchsatz.

Registered, buffered und un-buffered

Normalerweise sind Speichermodule nicht gepuffert. Bis einschließlich EDO

RAM gab es sogenannten "buffered RAM", er war mit

einem Puffer ausgestattet um den Fehlerfreien Ablauf bei vielen Signalen

auf einmal zu gewährleisten.

Seit der Einführung des SDRAMs gibt es einen solchen Puffer nicht mehr,

daher hat man

"Registered RAM" produziert, dabei wird der komplette

Ablauf um einen Taktzyklus verzögert

und somit ein fehlerfreierer Betrieb möglich.

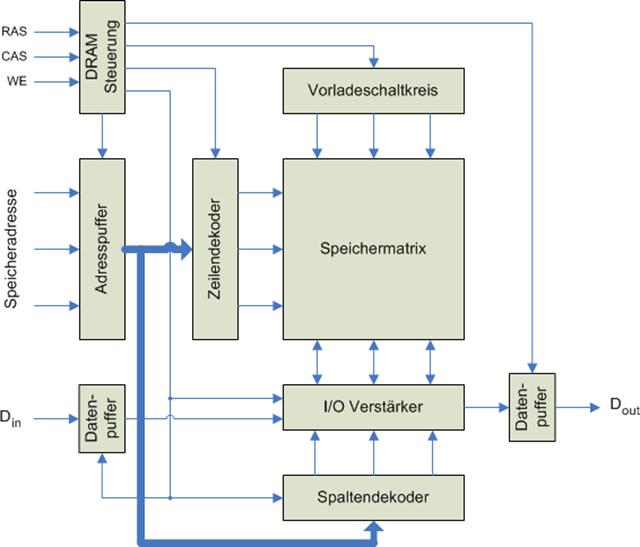

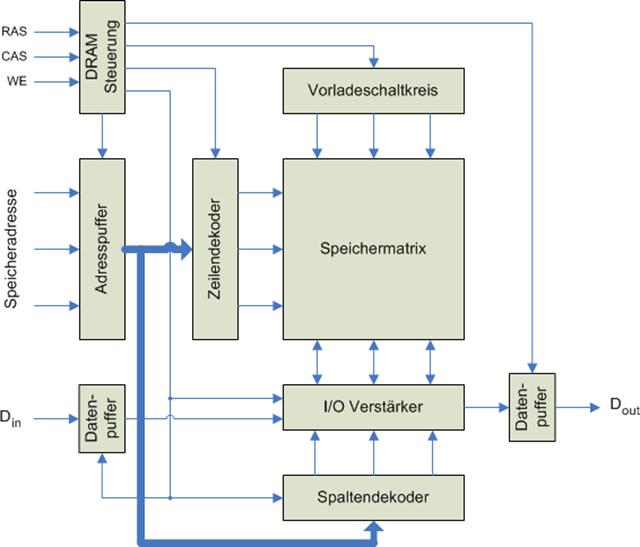

Speicherzugriff

Inderregel ist der Speicher-Controller ein Teil der

Northbridge und hat die Aufgabe Daten in den RAM zu schreiben, bzw. zu lesen.

Innerhalb des Speicherchips selbst sind die einzelnen

Bit Speicherzellen in Zeilen (Rows) und Spalten

(Columns) unterteilt und bilden somit ein Gitter bzw. Matrix.

Heutzutage verfügen Prozessoren über einen 32 Bit, bzw. 64 Bit Adressbus, damit können maximal 4GB, bzw. 16

Exabyte Speicher adressiert werden.

Um auf eine

spezielle Speicherzelle zugreifen zu können wird zuerst die Zeilen-Adresse an den Adressbus des

Speichers angelegt und das RAS (Row Adress Strobe) Signal gesetzt. Bis die

Spalten Adresse übertragen werden kann muss etwas

gewartet werden. Diesen Zeitraum

nennt man RAS-to-CAS Delay-Zeit.

Schließlich wird die Spalten-Adresse

übertragen, dabei wird das CAS (Column

Adress Strobe) Signal angelegt.

Nachdem nun die Speicherzelle angewählt wurde

vergeht wiederum etwas Zeit (CAS Latency) bis das Signal an

den

Ausgängen zur Verfügung steht. Wenn geschrieben werden soll wird das WE

Signal gesetzt. Immer wenn eine Zeile

gewechselt wird muss ebenfalls einige Taktzyklen abgewartet (RAS Prechage Time)

werden, dabei werden die durch das

lesen entladenen Kondensatoren

wieder geladen. Zuletzt spielt auch die RAS Active Time

eine Rolle, dabei es sich um eine

Mindestwartezeit die in einer Zeile verblieben

werden muss damit es zu keinem Datenverlust kommt.

Die besagten Zeiten werden auch Timings

genannt und werden häufig durch einen

Bindestrich getrennt angegeben, z.B. 2,5-3-3-7

1.

Ziffer: CAS Latency

2. Ziffer: RAS to CAS Latency

3. Ziffer: RAS Precharge

4. Ziffer: RAS Active Time

Dabei handelt es sich immer um Angaben in Taktzyklen. Allgemein kann man sagen das

niedrigere Timings immer

besser sind.

Zukünftiger

Speicher

Neben DDR3 wird auch an einer komplett neuen Speicherart geforscht, dem sogenannten

MRAM (Magneto-resistive Random Access Memory). Der große Vorteil ist das er nicht flüchtig ist. Aus dieser Tatsache ergeben sich wiederum komplett neue Möglichkeiten, es währe z.B.

möglich einen Computer einfach einzufrieren und später dort Weiterzumachen (Ahnlich des Ruhezustandes, jedoch

ohne merkbare Ladezeiten). Auch ein

Einsatz als lautloser und extrem schneller

Massenspeicher währe denkbar.

Zurzeit liegen die Zugriffszeiten jedoch noch bei 35 ns was deutlich langsamer ist als herk mmlicher SDRAM.

Zusätzlich ist auch die Fertigung sehr teuer,

so kosten 4MB Speicher 25 US-Doller.

Nur

eins kann man mit Sicherheit sagen, Arbeitsspeicher

lässt sich nur durch noch mehr

Arbeitsspeicher

ersetzen.

Quellen:

https://www.chip.de/c1_forum/thread.html?bwthreadid=535752

https://eu.shuttle.com/archive/de/simmdimm.htm https://wb.rus.uni-stuttgart.de/pc/hauptspeicher.asp

https://www.hardwaregrundlagen.de/oben08.htm

https://www.martinvogel.de/pc/ramfaq.txt

https://www3.planet-rcs.de/de/article/ram1/ https://www3.planet-rcs.de/de/article/ram2/ https://www3.planet-rcs.de/de/article/ram3/

https://www.pc-erfahrung.de/Index.html arbeitsspeicher_geschichte.html https://tomshardware.thgweb.de/2004/01/23/rauf_und_runter_einfluss_der_speichertimings_au f_die_performance/index.html

https://www.zdnet.de/glossar/0,39029897,70012277p-39001846q,00.htm

https://www.hardtecs4u.com/reviews/2002/speicherroundup/index6.php

https://www.informatik.fh-muenchen.de/~tensi/r-tech/techreal.pdf

https://wwwiaim.ira.uka.de/users/asfour/TI/TI-2/Vorlesung/skript2.pdf https://wikipedia.org

PC-Hardwarebuch (Hans-Peter Messmer,

Addison-Wesley Verlag, 1992) Alle Webseiten wurden im September

2006 abgerufen

Signal

Ablauf

Aufbau eines DRAM Chips

RAM Übersicht

|

Chip

|

Modul

|

Speichertakt

|

I/O-

Takt

|

Effektiver

Takt

|

Bandbreite

pro Modul

|

Bandbreite

Dual-Channel

|

|

SIMM

|

SIMM

|

~33

Mhz

|

~33

Mhz

|

~33

Mhz

|

~

33 MB/s

|

|

|

FPM

|

FPM

|

~33

Mhz

|

~33

Mhz

|

~33

Mhz

|

~

150 MB/s

|

|

|

EDO

|

EDO

|

~66

Mhz

|

~66

Mhz

|

~66

Mhz

|

~

396 MB/s

|

|

|

SD-66

|

PC-66

|

66

Mhz

|

66

Mhz

|

66

Mhz

|

0,53

GB/s

|

|

|

SD-100

|

PC-100

|

100

Mhz

|

100

Mhz

|

100

Mhz

|

0,8

GB/s

|

|

|

SD-133

|

PC-133

|

133

Mhz

|

133

Mhz

|

133

Mhz

|

1,06

GB/s

|

|

|

RD-600

|

PC-600

|

300

Mhz

|

300

Mhz

|

600

Mhz

|

1,2

GB/s

|

|

|

RD-710

|

PC-700

|

355

Mhz

|

355

Mhz

|

710

Mhz

|

1,42

GB/s

|

|

|

RD-800

|

PC-800

|

400

Mhz

|

400

Mhz

|

800

Mhz

|

1,6

GB/s

|

|

|

RD-

1066

|

PC-

1066

|

533

Mhz

|

533

Mhz

|

1066

Mhz

|

3,12

GB/s

|

|

|

RD-

1200

|

PC-

1200

|

600

MHz

|

600

Mhz

|

1200

Mhz

|

2,4

GB/s

|

|

|

RD-800

|

RIMM

3200

|

400

MHz

|

400

Mhz

|

800

Mhz

|

|

3,2

GB/s

|

|

RD-

1066

|

RIMM

4200

|

533

Mhz

|

533

Mhz

|

1066

Mhz

|

|

4,2GB/s

|

|

RD-

1200

|

RIMM

4800

|

600

Mhz

|

600

Mhz

|

1200

Mhz

|

|

4,8

GB/s

|

|

RD-

1600

|

RIMM

6400

|

800

MHz

|

800

Mhz

|

1600

Mhz

|

|

6,4

GB/s

|

|

RD-

2100

|

RIMM

8600

|

1066

Mhz

|

1066Mhz

|

2132

Mhz

|

|

8,6

GB/s

|

|

DDR-

200

|

PC-

1600

|

100

MHz

|

100

MHz

|

200

MHz

|

1,6

GB/s

|

3,2

GB/s

|

|

DDR-

266

|

PC-

2100

|

133

MHz

|

133

MHz

|

266

MHz

|

2,1

GB/s

|

4,2

GB/s

|

|

DDR-

333

|

PC-

2700

|

166

MHz

|

166

MHz

|

333

MHz

|

2,7

GB/s

|

5,4

GB/s

|

|

DDR-

400

|

PC-

3200

|

200

MHz

|

200

MHz

|

400

MHz

|

3,2

GB/s

|

6,4

GB/s

|

|

DDR2-

400

|

PC2-

3200

|

100

MHz

|

200

MHz

|

400

MHz

|

3,2

GB/s

|

6,4

GB/s

|

|

DDR2-

533

|

PC2-

4200

|

133

MHz

|

266

MHz

|

533

MHz

|

4,2

GB/s

|

8,4

GB/s

|

|

DDR2-

667

|

PC2-

5300

|

166

MHz

|

333

MHz

|

667

MHz

|

5,3

GB/s

|

10,6

GB/s

|

|

DDR2-

800

|

PC2-

6400

|

200

MHz

|

400

MHz

|

800

MHz

|

6,4

GB/s

|

12,8

GB/s

|

|

DDR3-

800

|

PC3-

6400

|

100

MHz

|

400

MHz

|

800

MHz

|

6,4

GB/s

|

12,8

GB/s

|

|

DDR3-

1066

|

PC3-

8500

|

133

MHz

|

533

MHz

|

1066

MHz

|

8,5

GB/s

|

17,0

GB/s

|

Geschwindigkeit

der Anbindung an den Speichercontroller

von CPU oder Mainboard

Effektiver Takt im Vergleich zu SDRAM

Copyright ©

2025 - Alle Rechte vorbehalten

AZreferate.com |

Verwenden sie diese referate ihre eigene arbeit zu schaffen. Kopieren oder herunterladen nicht einfach diese

# Hauptseite # Kontact / Impressum |